# PRODUCT SPECIFICATION FOR XY-DUAL AXIS ACCELEROMETER SCA1000 - D01

### **Table of Contents**

| 1 | General description                                     | 3  |

|---|---------------------------------------------------------|----|

|   | 1.1 Block diagram                                       | 3  |

|   | 1.2 SCA1000 family Accelerometer Features               | 3  |

| 2 | Electrical specifications                               | 4  |

|   | 2.1 Electrical Connection                               | 4  |

|   | 2.1.1 Recommended connection when SPI interface is used | 5  |

|   | 2.1.2 Recommended connection when analog output is used | 5  |

|   | 2.1.3 Recommended EMC protection circuitry              | 6  |

|   | 2.2 Absolute maximum ratings                            | 6  |

|   | 2.3 Electrical Specification of the SCA1000 – D01       | 7  |

|   | 2.3.1 Analog Output                                     | 7  |

|   | 2.3.2 Digital Output                                    | 9  |

| 3 | SPI Interface                                           | 10 |

|   | 3.1 DC characteristics of SPI interface                 | 12 |

|   | 3.2 AC characteristics of SPI interface                 | 13 |

|   | 3.3 SPI Commands                                        | 14 |

| 4 | Mechanical specification (Reference only)               | 16 |

|   | 4.1 Dimensions (Reference only)                         | 16 |

| 5 | Mounting                                                | 17 |

3/18

#### 1 **General description**

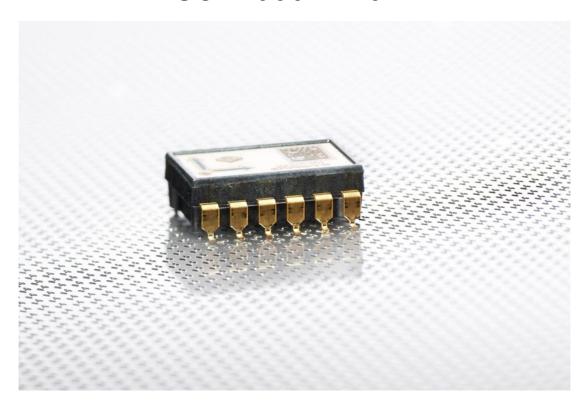

The SCA1000 accelerometer consists of two silicon bulk micro machined sensing element chips and a signal conditioning ASIC. The chips are mounted on a pre-molded package and wire bonded to appropriate contacts. The sensing elements and ASIC are protected with silicone gel and lid. The sensor has 12 SMD legs (Gull-wing type).

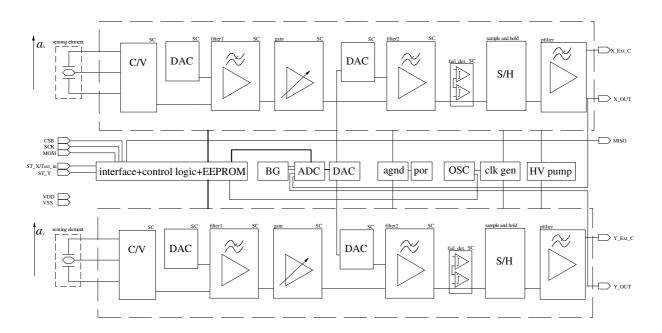

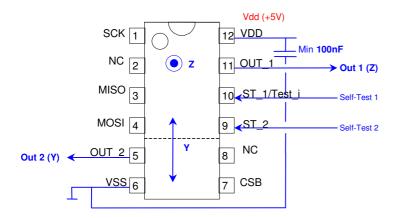

### **Block diagram** 1.1

Figure 1. Block diagram of the SCA1000

### 1.2 SCA1000 family Accelerometer Features

- Single +5V supply

- Two ratiometric analog outputs in relation to supply voltage (Vdd = 4.75....5.25V)

- Wide load driving capability

- Serial Peripheral Interface (SPI) compatible

- Provides digital output for both channels

- Supports testing and programming

- Non-volatile programming features

- Factory programmable filter settings (400Hz, 1 kHz, WB, Ext C)

- Offset and sensitivity calibration

- Linear temperature compensation

- Enhanced failure detection features

- True self test by deflecting the sensing elements' proof mass by electrostatic force. Deflection voltage is adjustable with two memory bits for both channels. The self-test is channel specific, and separately activated for both channels by digital on-off commands via dedicated pins or via SPI bus.

- Continuous sensing element interconnection failure check

# 2 Electrical specifications

### 2.1 Electrical Connection

The following is a typical requirement for electrical interface to the SCA1000. If special over voltage or reverse polarity protection is needed, please contact VTI Technologies for application information.

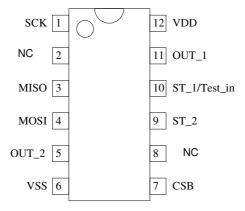

If self test (Pins 9 and 10) is not used, it should be left floating / grounded

| No. | Node           | I/O    | Description                                           |

|-----|----------------|--------|-------------------------------------------------------|

| 1   | SCK            | Input  | Serial clock                                          |

| 2   | NC             | NC     | NC                                                    |

| 3   | MISO           | Output | Master in slave out; data output                      |

| 4   | MOSI           | Input  | Master out slave in; data input                       |

| 5   | Out_2          | Output | Y axis Output (Ch 2)                                  |

| 6   | VSS            | Power  | Negative supply voltage (VSS)                         |

| 7   | CSB            | Input  | Chip select (active low)                              |

| 8   | NC             | NC     | NC                                                    |

| 9   | ST_2           | Input  | Self test input for Y axis (Ch 2)                     |

| 10  | ST_1 / Test_in | Input  | Self test input for X axis (Ch 1) / Analog test input |

| 11  | Out_1          | Output | X axis output (Ch 1)                                  |

| 12  | VDD            | Power  | Positive supply voltage (VDD)                         |

Figure 2. Pin layout and description of the SCA1000

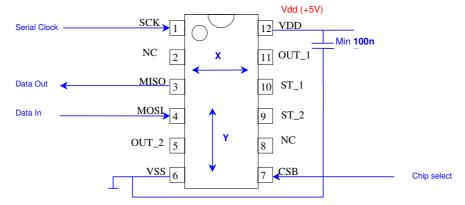

### 2.1.1 Recommended connection when SPI interface is used

Recommended SPI-Output connection on PCB

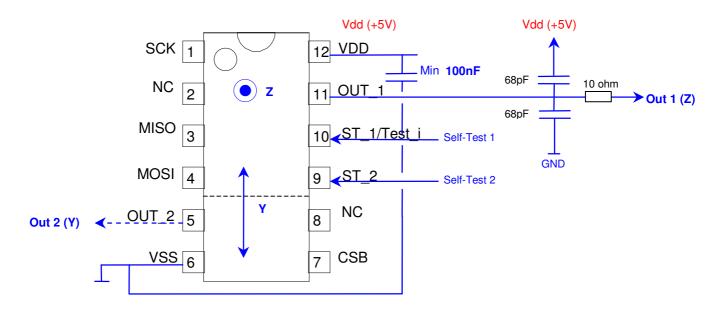

### 2.1.2 Recommended connection when analog output is used

When SCA1020 is used in Analog mode and the PCB is designed correctly the SCA610 / 620 and SCA1020 are interchangeable. If the PCB layout is designed for SCA1020, then SCA610 / 620 can be used for single axis applications. Pins 1, 2, 3, 4 and 8 can be connected to GND (pins 2 and 8 can be connected also to Vdd) but for the best EMC performance these pins should be left floating. CSB pin can be pulled up but it is recommended to left floating. The output of SCA610 / 620 corresponds to the output of channel 1 in the SCA1020

Recommended Analog output connection on PCB

SCA610 or SCA620 connected to the SCA1020 lay-out

### 2.1.3 Recommended EMC protection circuitry

The purpose of the following recommendation is to give generic EMC protection guidelines for the SCA1020. EMC susceptibility is highly dependent on the PCB layout and therefore the component values given here can be different depending on the actual PCB layout. With the following circuitry and properly designed PCB the part will pass 200V/m EMC susceptibility tests.

Please note that only channel 1 output protection circuitry is presented. Similar kind of circuit must be also at the channel 2 output.

Recommended EMC protection circuitry

### 2.2 Absolute maximum ratings

Supply voltage  $(V_{DD})$  -0.3 V to +5.5V (continuous)

-0.3V to 7V (5 seconds during 1 minutes cycle)

Voltage at input / output pins -0.3V to  $(V_{DD} + 0.3V)$

**ESD**

HBM (Human Body Model) ±2kV CDM (Charged Device Model) ±500V

Storage temperature  $-55^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$ Operating temperature  $-40^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$

Mechanical shock Drop from 1 meter on a concrete surface.

# 2.3 Electrical Specification of the SCA1000 – D01 2.3.1 Analog Output

Vdd = 5.00V and ambient temperature (23 °C±5 °C) unless otherwise specified. .

| KPC <sup>(16</sup> | Parameter                                                                        | Condition                    | Min.  | Тур           | Max.   | Units           |

|--------------------|----------------------------------------------------------------------------------|------------------------------|-------|---------------|--------|-----------------|

|                    | X axis (Out_1) Measuring range (1                                                | Nominal                      | -1.7  |               | +1.7   | g <sup>(2</sup> |

|                    | Y axis (Out_2) Measuring range (1                                                | Nominal                      | -1.7  |               | +1.7   | g <sup>(2</sup> |

|                    | Supply voltage Vdd                                                               |                              | 4.75  | 5.0           | 5.25   | V               |

| <cc></cc>          | Current consumption                                                              | Vdd = 5 V; No load           |       |               | 5.0    | mA              |

|                    | Operating temperature                                                            |                              | -40   |               | +125   | °C              |

|                    | Resistive output load (Analog Output)                                            | Vout to Vdd or Vss           | 10    |               |        | kOhm            |

|                    | Capacitive load (Analog Output)                                                  | Vout to Vdd or Vss           |       |               | 20     | nF              |

|                    | Min. output voltage; Vdd = 5V                                                    | 10k from Vout to Vdd         | 0     |               | 0.25   | V               |

|                    | Max. output voltage; Vdd = 5V                                                    | 10k from Vout to Vss         | 4.75  |               | 5.00   | V               |

| <cc></cc>          | X axis (Out_1) Offset (output at 0g) (3, 13                                      | @ room temperature           |       | Vdd/2         | 0.00   | V               |

| <cc></cc>          | X axis (Out_1) Sensitivity (4, 13                                                | @ room temperature           |       | 0.24 x        |        | V/g             |

| 100/               | A data (dat_1) denotable                                                         | e room tomporaturo           |       | Vdd           |        | ,,9             |

| <sc></sc>          | X axis (Out_1) Offset Error (output at 0g) (5,                                   | -40+105°C                    | -80   | -             | +80    | mg              |

|                    | 13                                                                               |                              | -100  | -             | +100   |                 |

|                    | ) (6.13                                                                          | -40+125°C                    |       |               |        |                 |

| <sc></sc>          | X axis (Out_1) Sensitivity error (6, 13                                          | -40+105°C                    | _     | ±3            |        | %               |

|                    |                                                                                  | -40+125°C                    | -4    | -             | +4     |                 |

|                    | V : (0 + 0) 0" + ( + + + 0 ) (3.13                                               |                              |       | 1/11/0        |        |                 |

| <cc></cc>          | Y axis (Out_2) Offset (output at 0g) (3, 13<br>Y axis (Out_2) Sensitivity (4, 13 | @ room temperature           |       | Vdd/2         |        | V               |

| <cc></cc>          | Y axis (Out_2) Sensitivity                                                       | @ room temperature           |       | 0.24 x<br>Vdd |        | V/g             |

| <sc></sc>          | Y axis (Out_2) Offset Error (output at 0g) (5,                                   |                              | -80   | -             | +80    | ma              |

| <30>               | 13 Oliset Error (output at og)                                                   | -40+105°C                    | -100  | -             | +100   | mg              |

|                    |                                                                                  | -40+125°C                    | -100  | -             | +100   |                 |

| <sc></sc>          | Y axis (Out_2) Sensitivity error (6, 13                                          | -40+105°C                    |       | ±3            |        | %               |

|                    |                                                                                  | -40+125°C                    | -4    | -             | +4     |                 |

|                    | Typical non-linearity (7                                                         | Range = -1g+1g               | -20   | _             | +20    | mg              |

|                    | X axis (Out_1) Frequency response -3dB <sup>(8)</sup>                            | Trange = Tg+Tg               | 20    | 50            | 80     | Hz              |

|                    | V axis (Out 2) Frequency response -3dB <sup>(8)</sup>                            |                              | 20    | 50            | 80     | Hz              |

|                    | Y axis (Out_2) Frequency response -3dB <sup>(8)</sup> Ratiometric error (9)      | Vdd = 4.755.25V              | -2    | -             | 2      | %               |

| <sc></sc>          | Cross-axis sensitivity (10                                                       | @ room temperature           |       |               | 3.5    | %               |

| 100/               | Output noise (11                                                                 | From DC4kHz                  |       |               | 5      | mVrms           |

|                    | Start-up delay                                                                   | Reset and parity check       |       |               | 10     | ms              |

|                    | Self test input pull down current                                                | Vdd = 5V                     | 10    | 21            | 30     | μA              |

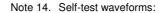

|                    | T1: T st-on <sup>(14</sup>                                                       | Self test ON period.         | 10    |               | 100    | •               |

|                    | TT. T St-Off                                                                     | Controlled externally by     | 10    |               | 100    | ms              |

|                    |                                                                                  | user                         |       |               |        |                 |

|                    | T2: Tsat.del. (14                                                                | Saturation delay. Time       |       |               | 20     | ms              |

|                    | 12. 13at.uci.                                                                    | when element beam            |       |               | 20     | 1113            |

|                    |                                                                                  | remains still out from       |       |               |        |                 |

|                    |                                                                                  | linear operating range.      |       |               |        |                 |

|                    | T3: T recov. (14                                                                 | Recovery time when           |       |               | 50     | ms              |

|                    |                                                                                  | element is back in linear    |       |               |        |                 |

|                    |                                                                                  | operating range              |       |               |        |                 |

|                    | T4: T stab. (14                                                                  | Stabilisation time, when     |       |               | 70     | ms              |

|                    | = T2+T3                                                                          | self test is released.       |       |               |        |                 |

|                    | T5: T r <sup>(14</sup>                                                           | Rise time during self test,  |       |               | 10     | ms              |

|                    |                                                                                  | when Vout reach V2           |       |               |        |                 |

|                    | V2 <sup>(14</sup>                                                                | Vout during self test        | 4.75  |               |        | V               |

|                    | V3 <sup>(14, 15</sup>                                                            | Stabilised output voltage    | 0.95* | V1            | 1.05 * |                 |

|                    |                                                                                  | after self test is released. | V1    |               | V1     | Ì               |

- Note 1. The measuring range is limited only by the sensitivity, offset and supply voltage rails of the device

- Note 2.  $1g = 9.82 \text{m/S}^2$

- Note 3. Offset specified as Voffset = Vout(0g) [V]. See note 13.

- Note 4. Sensitivity specified as  $Vsens = {Vout(+1g) Vout(-1g)}/2$  [V/g]. See note 13

- Note 5. Offset error specified as Offset Error = {Vout(0g) Vdd/2} / Vsens [g] Vsens = Nominal sensitivity Vdd/2 = Nominal offset See note 13.

- Note 6. Sensitivity error specified as Sensitivity Error = { [Vout(+1g) Vout(-1g)] / 2 Vsens} / Vsens x 100% [% ] Vsens = Nominal sensitivity See note 13.

- Note 7. From straight line through -1g and +1g.

- Note 8. The frequency response is determined by the sensing element's internal gas damping. The output has true DC (0Hz) response.

- Note 9. The ratiometric error is specified as.

$$RE = 100\% \times \left(1 - \frac{Vout(@Vx) \times \frac{5.00V}{Vx}}{Vout(@5V)}\right)$$

- Note 10. The cross-axis sensitivity determines how much acceleration, perpendicular to the measuring axis, couples to the output. The total cross-axis sensitivity is the geometric sum of the sensitivities of the two axes that are perpendicular to the measuring axis.

- Note 11. In addition, supply voltage noise couples to the output due to the ratiometric nature of the accelerometer.

- Note 12. The self-test will increase the output voltage. The output will go to Vdd rail. The purpose of the self-test is to check out the total functionality of the sensor. It is not meant for calibration or auto zeroing.

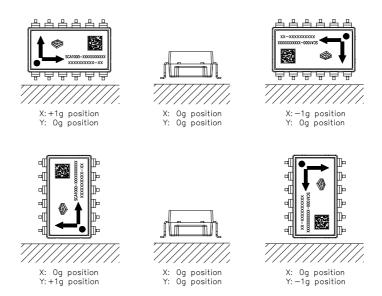

- Note 13. Measuring positions

Note 15. V1= Initial output Voltage before self-test activation

V3= Output voltage after self-test has been removed and after stabilization time. Please note that the error

band specified for V3 is to guarantee that the output is within 5% of the initial value after the specified stabilization time.

After longer time V1=V3.

Note 16 CC= Critical Characteristics. Must be 100% monitored during production SC=

Significant Characteristic. The process capability (Cpk) must be better than 1.33, which allows sample

based testing. If process is not capable the part will be 100% tested

# 2.3.2 Digital Output

Vdd = 5.00V and ambient temperature unless otherwise specified.

| Parameter                    | Condition | Min. | Тур | Max. | Units |

|------------------------------|-----------|------|-----|------|-------|

| Output load                  | @500kHz   |      |     | 1    | nF    |

| SPI clock frequency          |           |      |     | 500  | kHz   |

| Internal A/D conversion time |           |      |     | 150  | μs    |

| Data transfer time           | @500kHz   |      |     | 38   | μs    |

### 3 SPI Interface

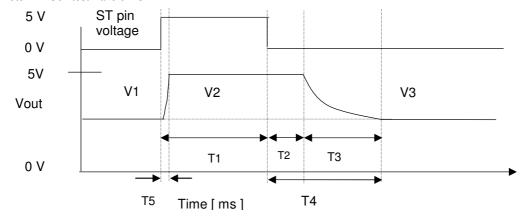

Serial peripheral interface (SPI) is a 4-wire synchronous serial interface. Data communication is enabled with low active Slave Select or Chip Select wire (CSB). Data is transmitted with 3-wire interface consisting of serial data input (MOSI), serial data output (MISO) and serial clock (SCK). Every SPI system consists of one master and one or more slaves, where the master is defined as the microcomputer that provides the SPI clock, and the slave is any integrated circuit that receives the SPI clock from the master.

Figure 4. Typical SPI connection

The SPI interface of this ASIC is designed to support almost any micro controller that uses software implemented SPI. However it is not designed to support any particular hardware implemented SPI found in many commercial micro controllers. Serial peripheral interface in this product is used in testing and calibration purposes as well as in the final application. In normal use some testing and calibration commands are disabled and have not been documented here. This ASIC operates always as a slave device in the master-slave operation mode. The data transfer between the master ( $\mu$ P test machine etc.) and ASIC is performed serially with four wire system.

| MOSI | master out slave in      | $\mu P 	o ASIC$          |

|------|--------------------------|--------------------------|

| MISO | master in slave out      | $ASIC \to \muP$          |

| SCK  | serial clock             | $\mu P \rightarrow ASIC$ |

| CSB  | chip select (low active) | $\mu P \rightarrow ASIC$ |

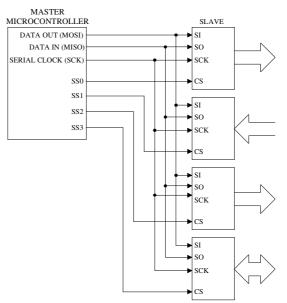

Each transmission starts with a falling edge on CSB and ends with the rising edge. During the transmission, commands and data are controlled by SCK and CSB according to the following rules:

- commands and data are shifted MSB first LSB last

- each output data/status-bits are shifted out on the falling edge of SCK (MISO line)

- each bit is sampled on the rising edge of SCK (MOSI line)

- after the device is selected with CSB going low, an 8-bit command is received. The command defines the operations to be performed

- the rising edge of CSB ends all data transfer and resets internal counter and command register

- if an invalid command is received, no data will be shifted into chip and the MISO will remain in high impedance state until the falling edge of CSB. This will reinitialize the serial communication.

- to be able to perform any other command than those listed in Table 1. *SPI commands*, the lock register content has to be set correctly. If other command is feed without correct lock register content, no data will be shifted into chip and the MISO will remain in high impedance state until the falling edge of CSB.

- data transfer to MOSI continues right after the command is received in all cases where data is to be written to ASIC's internal registers

- data transfer out from MISO starts with a falling edge of SCK right after the last bit of SPI command is sampled in on the rising edge of SCK

- maximum data transfer speed exceeds 500 kHz clock rate

SPI command can be an individual command or a combination of command and data. In the case of combined command and data, the input data follows uninterruptedly the SPI command and the output data is shifted out parallel with the input data.

Figure 5. One command and data transmission over the SPI

After power up the circuit starts up in measure mode. This is the operation mode that is used in the final application.

### 3.1 DC characteristics of SPI interface

Supply voltage is 5 V unless otherwise noted. Current flowing into the circuit have positive values.

| Parameter            | Conditions           | Symbol            | Min     | Тур      | Max     | Unit |  |  |  |

|----------------------|----------------------|-------------------|---------|----------|---------|------|--|--|--|

| Input terminal CSB   |                      |                   |         |          |         |      |  |  |  |

| Pull up current      | $V_{IN} = 0 V$       | I <sub>PU</sub>   | 13      | 22       | 35      | μΑ   |  |  |  |

| Input high voltage   |                      | $V_{IH}$          | 4       |          | Vdd+0.3 | V    |  |  |  |

| Input low voltage    |                      | $V_{IL}$          | -0.3    |          | 1       | V    |  |  |  |

| Hysteresis           |                      | $V_{HYST}$        |         | 0.23*Vdd |         | V    |  |  |  |

| Input capacitance    |                      | C <sub>IN</sub>   |         | 2        |         | рF   |  |  |  |

| Input terminal MOSI, | SCK                  |                   |         |          |         |      |  |  |  |

| Pull down current    | $V_{IN} = 5 V$       | I <sub>PD</sub>   | 9       | 17       | 29      | μΑ   |  |  |  |

| Input high voltage   |                      | $V_{IH}$          | 4       |          | Vdd+0.3 | V    |  |  |  |

| Input low voltage    |                      | $V_{IL}$          | -0.3    |          | 1       | V    |  |  |  |

| Hysteresis           |                      | $V_{HYST}$        |         | 0.23*Vdd |         | V    |  |  |  |

| Input capacitance    |                      | C <sub>IN</sub>   |         | 2        |         | рF   |  |  |  |

| Output terminal MISO |                      |                   |         |          |         |      |  |  |  |

| Output high voltage  | I > -1mA             | $V_{OH}$          | Vdd-0.5 |          |         | V    |  |  |  |

| Output low voltage   | I < 1 mA             | $V_{OL}$          |         | _        | 0.5     | V    |  |  |  |

| Tristate leakage     | $0 < V_{MISO} < Vdd$ | I <sub>LEAK</sub> |         | 5        | 100     | рА   |  |  |  |

Table 1. DC characteristics of SPI interface

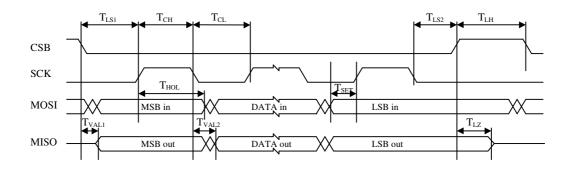

### 3.2 AC characteristics of SPI interface

| Parameter                                                                      | Conditions                       | Symbol           | Min | Тур | Max | Unit |

|--------------------------------------------------------------------------------|----------------------------------|------------------|-----|-----|-----|------|

| Terminal CSB, SCK                                                              |                                  |                  |     |     |     |      |

| Time from CSB (10%) to SCK (90%) <sub>1</sub>                                  |                                  | T <sub>LS1</sub> | 120 |     |     | ns   |

| Time from SCK (10%) to CSB (90%) <sub>1</sub>                                  |                                  | T <sub>LS2</sub> | 120 |     |     | ns   |

| Terminal SCK                                                                   |                                  |                  |     |     |     |      |

| SCK low time                                                                   | Load capacitance at MISO < 2 nF  | T <sub>CL</sub>  | 1   |     |     | μs   |

| SCK high time                                                                  | Load capacitance at MISO < 2 nF  | T <sub>CH</sub>  | 1   |     |     | μs   |

| Terminal MOSI, SCK                                                             |                                  |                  |     |     |     |      |

| Time from changing MOSI (10%, 90%) to SCK (90%) <sub>1</sub> . Data setup time |                                  | T <sub>SET</sub> | 30  |     |     | ns   |

| Time from SCK (90%) to changing MOSI (10%,90%) <sub>1</sub> . Data hold time   |                                  | T <sub>HOL</sub> | 30  |     |     | ns   |

| Terminal MISO, CSB                                                             |                                  |                  |     |     |     |      |

| Time from CSB (10%) to stable MISO (10%, 90%) <sub>1</sub> .                   | Load capacitance at MISO < 15 pF | $T_{VAL1}$       | 10  |     | 100 | ns   |

| Time from CSB (90%) to high impedance state of MISO <sub>1</sub> .             | Load capacitance at MISO < 15 pF | T <sub>LZ</sub>  | 10  |     | 100 | ns   |

| Terminal MISO, SCK                                                             |                                  |                  |     |     |     |      |

| Time from SCK (10%) to stable MISO (10%, 90%) <sub>1</sub> .                   | Load capacitance at MISO < 15 pF | $T_{VAL2}$       |     |     | 100 | ns   |

| Terminal CSB                                                                   |                                  |                  |     |     |     |      |

| Time between SPI cycles, CSB at high level (90%)                               |                                  | T <sub>LH</sub>  | 15  |     |     | μs   |

<sup>1</sup> not production tested

Table 2. AC characteristics of SPI interface

Figure 6. SPI bus timing diagram

### 3.3 SPI Commands

This SPI interface utilizes an 8-bit instruction (or command) register. The list of commands available to end-user is presented in Table 3.

| Command | Command  | Description:                                        |

|---------|----------|-----------------------------------------------------|

| name    | format   |                                                     |

| MEAS    | 00000000 | Measure mode (normal operation mode after power on) |

| RWTR    | 00001000 | Read and write temperature data register            |

| RDSR    | 00001010 | Read status register                                |

| RLOAD   | 00001011 | Reload NV data to memory output register            |

| STX     | 00001110 | Activate Self test for X-channel                    |

| STY     | 00001111 | Activate Self test for Y-channel                    |

| RDAX    | 00010000 | Read X-channel acceleration through SPI             |

| RDAY    | 00010001 | Read Y-channel acceleration through SPI             |

Table 3. SPI commands

**Measure mode (MEAS):** Standard operation mode after power-up. During normal operation, MEAS command is exit command from Self-Test.

Read and write temperature data register (RWTR): Temperature data register can be read during normal operation without affecting the circuit operation. Temperature data register is loaded in every 150  $\mu$ s, and the load operation is disabled whenever the CSB signal is low, hence CSB has to stay high at least 150  $\mu$ s prior the RWTR command in order to guarantee correct data. The data transfer is as presented in Figure 5 and data is transferred MSB first. In normal operation, it doesn't matter what data is written to temperature data register during RWTR command and hence all zeros is recommended.

**Read status register (RDSR):** Read status register command provides access to the status register. Status register format is shown in Table 4. Bold values in Definition column are the expected values during normal operation.

| Bit    | Definition                                    |  |  |

|--------|-----------------------------------------------|--|--|

| Bit 3  | Bit 3 = 0 Parity check hasn't detected errors |  |  |

| (PERR) | Bit 3 = 1 Parity error detected               |  |  |

| Bit 2  | Bit 2 = 0 Analog test mode isn't active       |  |  |

| (TEST) | Bit 2 = 1 Analog test mode is active          |  |  |

| Bit 1  | Bit 1 = 0 Lock register is open               |  |  |

| (LOCK) | Bit 1 = 1 Lock register is locked             |  |  |

| Bit 0  | Bit 0 = 0 circuit is not in power down mode   |  |  |

| (PD)   | Bit 0 = 1 circuit is in power down mode       |  |  |

Table 4. Status register bit definitions

**Reload NV data to memory output register (RLOAD):** Reads NV data from EEPROM to the memory output register.

**Self test for X-channel (STX):** STX command activates the circuit's self test function for the X-channel. Internal charge pump is activated and high voltage is applied to the X-

channel acceleration sensor element electrode. This causes electrostatic force, which deflects the beam of the sensing element and simulates the acceleration to the positive direction. X-channel self-test is de-activated by giving MEAS command.

**Self test for Y-channel (STY):** STY command activates the circuit's self test function for the Y-channel. Internal charge pump is activated and high voltage is applied to the Y-channel acceleration sensor element electrode. This causes electrostatic force, which deflects the beam of the sensing element and simulates the acceleration to the positive direction. Y-channel self-test is de-activated by giving MEAS command.

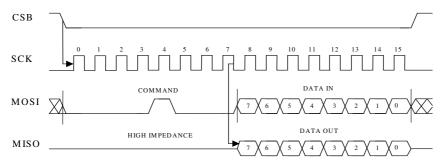

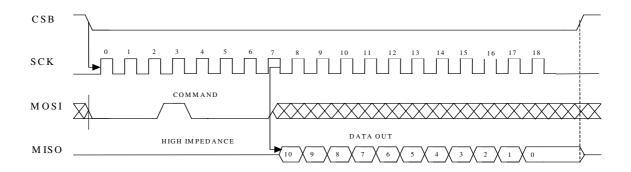

**Read X-channel acceleration (RDAX):** RDAX command provides access to AD converted X-channel acceleration signal stored in acceleration data register X. During normal operation acceleration data register X is loaded in every 150 μs, and the load operation is disabled whenever the CSB signal is low, hence CSB has to stay high at least 150 μs prior the RDAX command in order to guarantee correct data. Data output is an 11-bit digital word, which is feed out MSB first and LSB last. (See Figure 7).

Figure 7. RDAX command and data transmission over the SPI

**Read Y-channel acceleration (RDAY):** RDAY command provides access to AD converted Y-channel acceleration signal which is stored in acceleration data register Y. During normal operation acceleration data register Y is loaded in every 150 μs and the load operation is disabled whenever the CSB signal is low, hence CSB has to stay high at least 150 μs prior the RDAY command in order to guarantee correct data. Data output is an 11-bit digital word, which is feed out MSB first and LSB last

Detailed information on all SPI commands is presented in document *IC008 Dual Axis Acceleration Sensor ASIC*, *Digital Specification*.

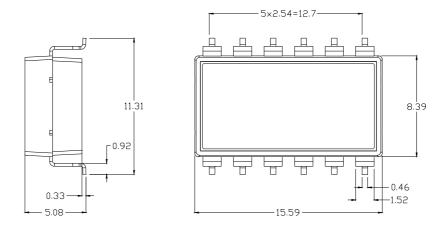

### 4 Mechanical specification (Reference only)

Lead frame material: Copper

Plating: Nickel followed by Gold

Solderability: JEDEC standard: JESD22-B102-C

**<CC>** Co-planarity error 0.1mm max.

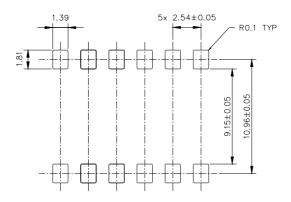

### 4.1 Dimensions (Reference only)

Figure 8. Mechanical dimensions of the SCA1000

### 5 Mounting

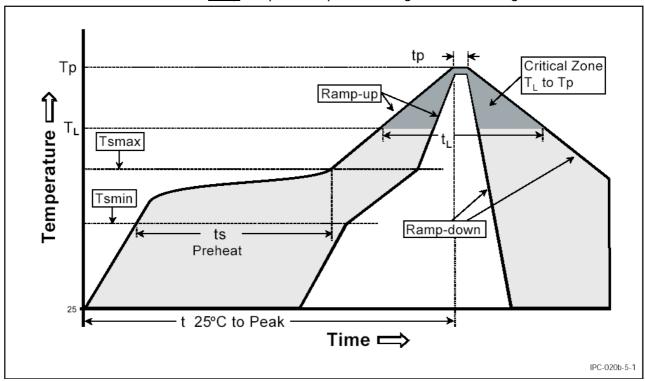

The SCA1000 is suitable for Sn-Pb eutectic and Pb- free soldering process and mounting with normal SMD pick-and-place equipment.

Recommended SCA1000 body temperature profile during reflow soldering:

| Profile feature                                             | Sn-Pb Eutectic Assembly | Pb-free Assembly |

|-------------------------------------------------------------|-------------------------|------------------|

| Average ramp-up rate                                        | 3 ℃/second max.         | 3°C/second max.  |

| (T <sub>L</sub> to T <sub>P</sub> )                         |                         |                  |

| Preheat                                                     |                         |                  |

| - Temperature min (T <sub>smin</sub> )                      | 100℃                    | 150℃             |

| - Temperature max (T <sub>smax</sub> )                      | 150℃                    | 200℃             |

| - Time (min to max) (ts)                                    | 60-120 seconds          | 60-180 seconds   |

| Tsmax to T <sub>L</sub>                                     |                         | 3°C/second max   |

| - Ramp up rate                                              |                         |                  |

| Time maintained above:                                      |                         |                  |

| - Temperature (T <sub>L</sub> )                             | 183℃                    | 217℃             |

| - Time (t <sub>L</sub> )                                    | 60-150 seconds          | 60-150 seconds   |

| Peak temperature (T <sub>P</sub> )                          | 240 +0/-5℃              | 250 +0/-5℃       |

| Time within 5℃ of actual Peak Temperature (T <sub>P</sub> ) | 10-30 seconds           | 20-40 seconds    |

| Ramp-down rate                                              | 6°C/second max          | 6°C/second max   |

| Time 25° to Peak temperature                                | 6 minutes max           | 8 minutes max    |

Figure 9. Recommended SCA1000 body temperature profile during reflow soldering. Ref. IPC/JEDEC J-STD-020B.

Note. Preheating time and temperatures according to solder paste manufacturer.

Component body temperature during the soldering should be measured from the body of the component.

The Moisture Sensitivity Level of the part is 3 according to the IPC/JEDEC J-STD-020B. The part should be delivered in a dry pack. The manufacturing floor time (out of bag) in the customer's end is 168 hours.

Maximum soldering temperature is 250°C/40sec.

Figure 10. Recommended PCB lay-out

### Notes:

- It is important that the part is parallel to the PCB plane and that there is no angular alignment error from intended measuring direction during assembly process.

- 1° mounting alignment error will increase the cross-axis sensitivity by 1.7%

- 1 ° mounting alignment error will change the output by 17mg

- To achieve the highest accuracy and to minimize resonance, it is recommended to glue the accelerometer to the PCB before soldering

- · Wave soldering is not recommended.

- A supply voltage by-pass capacitor (>100nF) must be used and located as close as possible to the Vdd and GND pins.

- Note: When the accelerometer is oriented in such a way that the arrow points toward the

earth, the output will decrease. Please also note that you can rotate the part around the

measuring axis for optimum mounting location.