# **1.8 V/3.0 V Dual SIM/SAM/** Smart Card Power Supply and Level Shifter

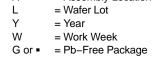

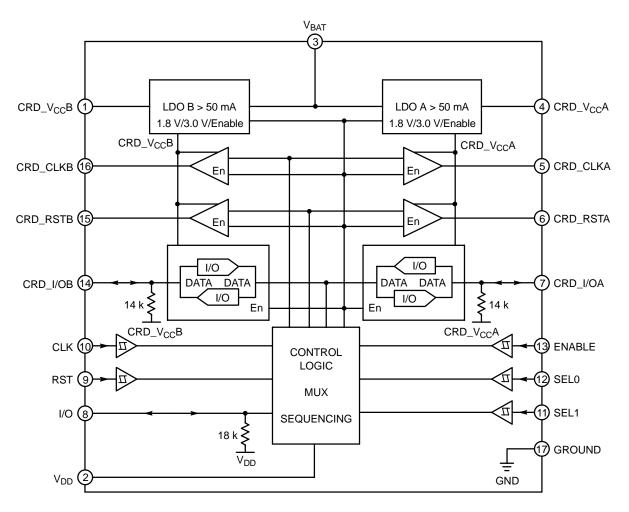

The NCN4557 is a dual interface analog circuit designed to translate the voltages between SIM, SAM or Smart Cards and a microcontroller (or similar control device). It integrates two LDOs for power conversion and three level shifters per channel allowing the management of two independent chip cards. The device fulfills the ISO7816 and EMV smart card interface requirements as well as the GSM and 3G mobile standard. Due to a built–in sequencer, the device enables automatic activation and deactivation. Through the ENABLE pin a low current shutdown mode can be activated extending the battery life.

The card power supply voltage (1.8 V or 3.0 V) and the card socket A or B are selected using two dedicated pins (SEL0 & SEL1).

# Features

- Supports 1.8 V or 3.0 V Operating SIM/SAM/Smart Cards

- The LDOs are able to Supply more than 50 mA Under 1.8 V and 3.0 V

- Built-in Active and Passive Pullup Resistor for I/O and CRD\_IOA/B Pins in Both Directions

- All Pins are Fully ESD Protected According to ISO-7816 Specifications – ESD Protection on Card Pins in Excess of 8.0 kV (JEDEC HBM)

- Built-in Sequencer for Activation and Deactivation

- Supports up to more than 5.0 MHz Clock

- Very Compact Low–Profile 3x3 QFN–16 Package

- These are Pb–Free Devices\*

# Applications

- SIM Card Interface Circuit for 2G, 2.5G and 3G Mobile Phones

- Wireless PC/Laptop Cards (PCMCIA Cards)

- POS Terminals (SAM Card Interfaces)

- Smart Card Readers

# **ON Semiconductor®**

http://onsemi.com

#### **ORDERING INFORMATION**

See detailed ordering and shipping information in the package dimensions section on page 11 of this data sheet.

\*For additional information on our Pb–Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

1.8 V/3 V SIM/Smart Card

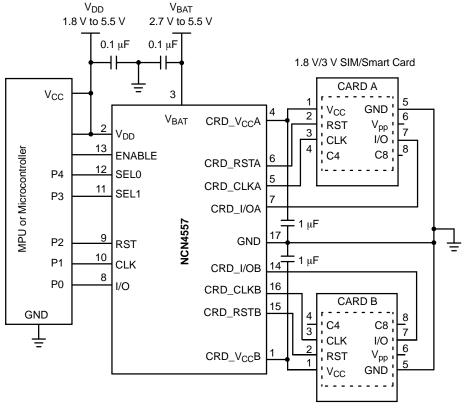

Figure 2. QFN-16 Pinout (Top View)

Figure 3. NCN4557 Block Diagram

# **PIN DESCRIPTIONS**

| PIN | Name                  | Туре              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----|-----------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | CRD_V <sub>CC</sub> B | POWER             | This pin is connected to the Card power supply pin (C1) (Card B). The corresponding LDO is programmable using the pins SEL0, SEL1 and ENABLE to provide 1.8 V, 3.0 V or 0 V (disable). $CRD_{VCC}B$ can not be active when $CRD_{VCC}A$ is active and conversely.                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 2   | V <sub>DD</sub>       | POWER             | This pin is connected to the controller power supply. It configures the level shifter input stage to accept the signal coming from the microcontroller. A 0.1 $\mu$ F capacitor shall be used to bypass the power supply voltage. When V <sub>DD</sub> is below 1.5 V typical CRD_V <sub>CC</sub> A and B are disabled; the NCN4557 comes into a shutdown mode.                                                                                                                                                                                                                                                                                                                              |

| 3   | V <sub>BAT</sub>      | POWER             | DC/DC converter power supply input shared by the LDOs A & B. This pin has to be by<br>passed by a 0.1 $\mu F$ capacitor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 4   | CRD_V <sub>CC</sub> A | POWER             | This pin is connected to the Card power supply pin (C1) (Card A). The corresponding LDO is programmable using the pins SEL0, SEL1 and ENABLE to provide 1.8 V, 3.0 V or 0 V (disable). CRD_V <sub>CC</sub> A can not be active when CRD_V <sub>CC</sub> B is active and conversely.                                                                                                                                                                                                                                                                                                                                                                                                          |

| 5   | CRD_CLKA              | OUTPUT            | This pin is connected to the clock pin (C3) of the card connector A. The clock (CLK) signal comes from the external clock generator (standalone clock source or microcontroller). The internal level shifter adapts the voltage levels CLK to CRD_CLKA. An internal active pull– down NMOS device maintains this pin to Ground during either the CRD_V <sub>CC</sub> A start–up sequence, or when CRD_V <sub>CC</sub> A = 0 V.                                                                                                                                                                                                                                                               |

| 6   | CRD_RSTA              | OUTPUT            | This pin is connected to the RESET pin (C2) of the card connector A. A level translator adapts the RESET signal from the microcontroller to the external card A. The output current is internally limited to 15 mA max. Similarly to the CRD_CLK A or B pins this pin is maintained Low when $CRD_V_{CC}A = 0$ V and during the corresponding LDO transient phase of power–up.                                                                                                                                                                                                                                                                                                               |

| 7   | CRD_I/OA              | INPUT /<br>OUTPUT | This pin handles the connection to the serial I/O pin (C7) of the card connector A. A bidirectional level translator adapts the serial I/O signal between the card and the micro–controller. A 14 k $\Omega$ (typical) pull–up resistor provides a High Impedance state to the card I/O link; during the operating phase, a dynamic pull–up circuit is activated making the CRD_I/OA rise time compliant with the ISO7816, EMV, GSM and related standards. An internal active pull–down MOS device forces this pin to Ground during either the CRD_V <sub>CC</sub> A start–up sequence or when CRD_V <sub>CC</sub> A = 0 V. The CRD_I/OA pin is internally limited by a 15 mA max current.   |

| 8   | I/O                   | INPUT /<br>OUTPUT | This pin is connected to an external microcontroller or cellular phone management unit (Baseband circuit or PMU). A bidirectional level translator adapts the serial I/O signal between the smart card A or B and the controller. Only one card, the selected card, communicates through the bidirectional I/O interface. A built–in 18 k $\Omega$ typical resistor provides a high impedance state when the interface is not activated. An additional dynamic pullup circuit accelerates the I/O rise time making the bidirectional channel perfectly balanced in regards to the standard rise time requirements.                                                                           |

| 9   | RST                   | INPUT             | The RESET signal present at this pin is connected to the card through the internal level shifter which translates the levels according to the CRD_V <sub>CC</sub> A or B programmed value.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 10  | CLK                   | INPUT             | The clock signal, coming from the external controller, must have a Duty Cycle within the Min/Max values defined by the specification (typically 50%). The built–in level shifter translates the input signal to the external card CLK input.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 11  | SEL1                  | INPUT             | SEL1 allows the selection of the Card A or B (Table 1).<br>SEL1 = Low → Card A selected<br>SEL1 = High → Card B selected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 12  | SEL0                  | INPUT             | $ \begin{array}{l} SEL0 \text{ allows programming } CRD_{V_{CC}A} \text{ or } B \ (1.8 \ V \ \text{or } 3.0 \ V) \ (Table 1). \\ SEL0 = Low \to CRD_{V_{CC}}A/B = 1.8 \ V \\ SEL0 = High \to CRD_{V_{CC}}A/B = 3.0 \ V \\ \end{array} $                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 13  | ENABLE                | INPUT             | Power Up and Down pin:<br>ENABLE = Low → Low current shutdown mode activated<br>ENABLE = High → Normal Operation<br>A Low level on this pin switches off the card interface.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 14  | CRD_I/OB              | INPUT /<br>OUTPUT | This pin handles the connection to the serial I/O pin (C7) of the card connector B. A bidirectional level translator adapts the serial I/O signal between the card and the micro–controller. A 14 k $\Omega$ (typical) pull–up resistor provides a High Impedance state to the card I/O link; during the operating phase a dynamic pull–up circuit is activated making the CRD_I/OB rise time compliant with the ISO7816, EMV, GSM and related standards. An internal active pulldown MOS device forces this pin to Ground during either the CRD_V <sub>CC</sub> B start–up sequence or when CRD_V <sub>CC</sub> B = 0 V. The CRD_I/OB pin is internally limited by a 15 mA maximum current. |

| 15  | CRD_RSTB              | OUTPUT            | This pin is connected to the RESET pin of the card connector B. A level translator adapts the RESET signal from the microcontroller to the external card B. The output current is internally limited by a 15 mA max current. Similarly to the CRD_CLK A or B pins this pin is maintained Low when CRD_V <sub>CC</sub> B = 0 V and during the corresponding LDO transient phase of powerup.                                                                                                                                                                                                                                                                                                   |

| 16  | CRD_CLKB              | OUTPUT            | This pin is connected to the clock pin (C3) of the card connector B. The clock (CLK) signal comes from the external clock generator (standalone clock source or microcontroller). The internal level shifter adapts the voltage levels CLK to CRD_CLKB. An internal active pull down NMOS device maintains this pin to Ground during either the CRD_V <sub>CC</sub> B start–up sequence, or when CRD_V <sub>CC</sub> B = 0 V.                                                                                                                                                                                                                                                                |

| 17  | GND                   | GND               | This pin number is the Exposed Pad which is the electrical Ground of the device. It must be soldered to the PCB ground plane.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

### ATTRIBUTES

| Characteristics                                        | Values               |  |  |  |

|--------------------------------------------------------|----------------------|--|--|--|

| ESD protection                                         |                      |  |  |  |

| Human Body Model (HBM):                                |                      |  |  |  |

| Card Pins (1, 4, 5, 6, 7, 14, 15, 16 & 17) (Note 1)    | 8 kV                 |  |  |  |

| All Other Pins (Note 1)                                | 2 kV                 |  |  |  |

| Machine Model (MM):                                    |                      |  |  |  |

| Card Pins (1, 4, 5, 6, 7, 14, 15, 16 & 17)             | 600 V                |  |  |  |

| All Other Pins                                         | 200 V                |  |  |  |

| Charged Device Model (CDM):                            |                      |  |  |  |

| Card Pins (1, 4, 5, 6, 7, 14, 15, 16 & 17)             | 2 kV                 |  |  |  |

| All Other Pins                                         | 400 V                |  |  |  |

| Moisture sensitivity (Note 2) QFN-16                   | Level 1              |  |  |  |

| Flammability Rating Oxygen Index: 28 to 34             | UL 94 V–0 @ 0.125 in |  |  |  |

| Meets or exceeds JEDEC Spec EIA/JESD78 IC Latchup Test |                      |  |  |  |

Human Body Model (HBM): R =1500 Ω, C = 100 pF.

For additional information, see Application Note AND8003/D.

### MAXIMUM RATINGS

| Rating                                                                                                       | Symbol                             | Value                                                       | Unit       |

|--------------------------------------------------------------------------------------------------------------|------------------------------------|-------------------------------------------------------------|------------|

| LDO Power Supply Voltage                                                                                     | V <sub>BAT</sub>                   | $-0.5 \le V_{BAT} \le 6$                                    | V          |

| Power Supply Microcontroller Side                                                                            | V <sub>DD</sub>                    | $-0.5 \le V_{DD} \le 6$                                     | V          |

| External Card Power Supply                                                                                   | CRD_V <sub>CC</sub>                | $-0.5 \le CRD\_V_{CC} \le 6$                                | V          |

| Digital Input Pins                                                                                           | V <sub>in</sub>                    | –0.5 ≤ V <sub>in</sub> ≤ V <sub>DD</sub> + 0.5<br>but < 6.0 | V          |

|                                                                                                              | l <sub>in</sub>                    | ±5                                                          | mA         |

| Digital Output Pins                                                                                          | V <sub>out</sub>                   | $-0.5 \leq V_{out} \leq V_{DD} + 0.5$                       | V          |

|                                                                                                              | l <sub>out</sub>                   | but < 6.0<br>± 10                                           | mA         |

| CRD Output Pins                                                                                              | V <sub>out</sub>                   | $-0.5 \le V_{out} \le CRD_V_{CC} + 0.5$<br>but < 6.0        | V          |

| CRD_I/O & CRD_RST Pins<br>CRD_CLK Pin                                                                        | l <sub>out</sub>                   | 15 (Internally Limited)<br>70 (Internally Limited)          | mA         |

| QFN-16 Low Profile package<br>Power Dissipation @ $T_A = +85^{\circ}C$<br>Thermal Resistance Junction-to-Air | P <sub>D</sub><br>R <sub>0JA</sub> | 450<br>90                                                   | mW<br>°C/W |

| Operating Ambient Temperature Range                                                                          | T <sub>A</sub>                     | -40 to +85                                                  | °C         |

| Operating Junction Temperature Range                                                                         | TJ                                 | -40 to +125                                                 | °C         |

| Maximum Junction Temperature                                                                                 | T <sub>Jmax</sub>                  | +125                                                        | °C         |

| Storage Temperature Range                                                                                    | T <sub>stg</sub>                   | -65 to + 150                                                | °C         |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

# **POWER SUPPLY SECTION** (-40°C to +85°C)

| Pin     | Symbol                     | Rating                                                                                                                                                                                                                                                                                                                                                                                                                           | Min          | Тур                  | Max                  | Unit |

|---------|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|----------------------|----------------------|------|

| 3       | V <sub>BAT</sub>           | Power Supply                                                                                                                                                                                                                                                                                                                                                                                                                     | 2.7          |                      | 5.5                  | V    |

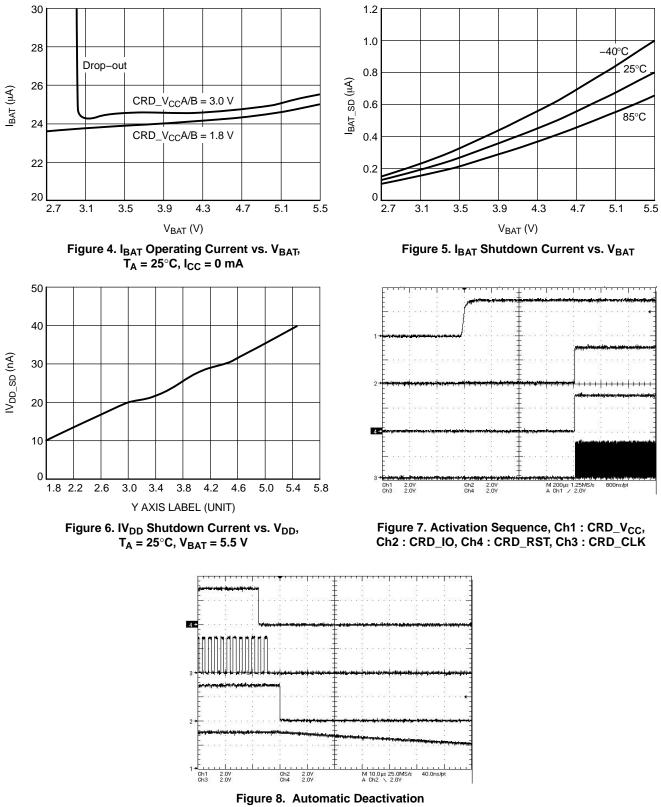

| 3       | I <sub>VBAT</sub>          | $\begin{array}{l} \label{eq:constraint} Operating current\\ CRD_V_{CC}A = 3.0 \text{ V}, CRD_V_{CC}B = 0 \text{ V}, I_{CC}A \& B = 0 \text{ mA}\\ CRD_V_{CC}A = 1.8 \text{ V}, CRD_V_{CC}B = 0 \text{ V}, I_{CC}A \& B = 0 \text{ mA}\\ CRD_V_{CC}A = 0 \text{ V}, CRD_V_{CC}B = 3.0 \text{ V}, I_{CC}A \& B = 0 \text{ mA}\\ CRD_V_{CC}A = 0 \text{ V}, CRD_V_{CC}B = 1.8 \text{ V}, I_{CC}A \& B = 0 \text{ mA}\\ \end{array}$ |              | 26<br>25<br>26<br>25 | 80<br>80<br>80<br>80 | μΑ   |

| 3       | I <sub>VBAT_SD</sub>       | Shutdown current – ENABLE = Low                                                                                                                                                                                                                                                                                                                                                                                                  |              |                      | 3                    | μΑ   |

| 2       | V <sub>DD</sub>            | Operating Voltage                                                                                                                                                                                                                                                                                                                                                                                                                | 1.8          |                      | 5.5                  | V    |

| 2       | I <sub>VDD</sub>           | Operating Current (CLK & RST Low)                                                                                                                                                                                                                                                                                                                                                                                                |              | 0.1                  | 2                    | μΑ   |

| 2       | I <sub>VDD_SD</sub>        | Shutdown Current – ENABLE = Low                                                                                                                                                                                                                                                                                                                                                                                                  |              | 0.05                 | 1                    | μΑ   |

| 2       | V <sub>DD</sub>            | Undervoltage Lockout                                                                                                                                                                                                                                                                                                                                                                                                             | 0.6          |                      | 1.5                  | V    |

| 1,4     | CRD_V <sub>CC</sub> A or B | 3.0 V Mode, $V_{BAT}$ = 3.3 V to 5.5 V, $I_{CRD_VCC}$ = 0 mA to 50 mA<br>1.8 V Mode, $V_{BAT}$ = 2.7 V to 5.5 V, $I_{CRD_VCC}$ = 0 mA to 50 mA                                                                                                                                                                                                                                                                                   | 2.75<br>1.65 | 3.0<br>1.8           | 3.25<br>1.95         | V    |

| 1,4     | I <sub>CRD_VCC_SC</sub>    | Short –Circuit Current – $CRD_V_{CC}$ Shorted to GND, $T_A = 25^{\circ}C$                                                                                                                                                                                                                                                                                                                                                        |              | 50                   | 175                  | mA   |

| 7,13,14 |                            | Channel Turn–on Time $I_{CC}A$ or B = 0 mA, ENABLE rise edge to CRD_I/OA or B rise edge                                                                                                                                                                                                                                                                                                                                          |              | 0.8                  | 2.5                  | ms   |

NOTE: Device will meet the specifications after thermal equilibrium has been established when mounted in a test socket or printed circuit board with maintained transverse airflow greater than 500 lfpm. Electrical parameters are guaranteed only over the declared operating temperature range. Functional operation of the device exceeding these conditions is not implied. Device specification limit values are applied individually under normal operating conditions and not valid simultaneously.

# DIGITAL INPUT/OUTPUT SECTION CLK, RST, I/O, ENABLE, SEL0, SEL1 (-40°C to + 85°C)

| Pin               | Symbol                                     | Rating                                                                                                                                                | Min                    | Тур | Max                                       | Unit |

|-------------------|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-----|-------------------------------------------|------|

| 9,10              | V <sub>IH</sub><br>V <sub>IL</sub>         | High Level Input Voltage (RST, CLK)<br>Low Level Input Voltage (RST, CLK)                                                                             | 0.85 * V <sub>DD</sub> |     | V <sub>DD</sub><br>0.15 * V <sub>DD</sub> | V    |

| 11,12,13          | V <sub>IH</sub><br>V <sub>IL</sub>         | High Level Input Voltage (ENABLE, SEL0, SEL1)<br>Low Level Input Voltage (ENABLE, SEL0, SEL1)                                                         | 0.85 * V <sub>DD</sub> |     | V <sub>DD</sub><br>0.15 * V <sub>DD</sub> | V    |

| 9,10,11,<br>12,13 | I <sub>IH</sub> , I <sub>IL</sub>          | Input current (RST, CLK, ENABLE, SEL0, SEL1)                                                                                                          | -1                     |     | 1                                         | μΑ   |

| 8                 | V <sub>OH_I/O</sub><br>V <sub>OL_I/O</sub> | High Level Output Voltage (CRD_ I/O = CRD_V <sub>CC</sub> , $I_{OH_I/O}$ =-20 µA)<br>Low Level Output Voltage (CRD_ I/O = 0 V, $I_{OL_I/O}$ = 500 µA) | 0.75 * V <sub>DD</sub> |     | V <sub>DD</sub><br>0.3                    | V    |

| 8                 | t <sub>R</sub> , t <sub>F</sub>            | Rise and Fall times (I/O), C <sub>out</sub> = 30 pF                                                                                                   |                        |     | 0.8                                       | μS   |

| 8                 | R <sub>pu_l/O</sub>                        | I/0 Pullup Resistor                                                                                                                                   | 12                     | 18  | 24                                        | kΩ   |

NOTE: Device will meet the specifications after thermal equilibrium has been established when mounted in a test socket or printed circuit board with maintained transverse airflow greater than 500 lfpm. Electrical parameters are guaranteed only over the declared operating temperature range. Functional operation of the device exceeding these conditions is not implied. Device specification limit values are applied individually under normal operating conditions and not valid simultaneously.

# CARD INTERFACE SECTION (-40°C to +85°C)

| Pin  | Symbol                  | Rating                                                                                                                                                                                                                                                                                                                                                         | Min                                       | Тур | Max                                          | Unit                      |

|------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|-----|----------------------------------------------|---------------------------|

| 6,15 | CRD_RSTA<br>CRD_RSTB    | $\begin{array}{l} \mbox{CRD}\_V_{CC} = +3 \ V \\ \mbox{Output RESET } V_{OH} @ \ ICRD\_rst = -20 \ \mu A \\ \mbox{Output RESET } V_{OL} @ \ ICRD\_rst = +200 \ \mu A \\ \mbox{Output RESET Rise Time } @ \ C_{out} = 30 \ pF \\ \mbox{Output RESET Fall Time } @ \ C_{out} = 30 \ pF \end{array}$                                                              | 0.9 * CRD_V <sub>CC</sub><br>0            |     | CRD_V <sub>CC</sub><br>0.3<br>0.8<br>0.8     | V<br>V<br>μs<br>μs        |

|      |                         | $\begin{array}{l} CRD_V_{CC} = +1.8 \text{ V} \\ & Output \ RESET \ V_{OH} \ @ \ ICRD_rst = -20 \ \muA \\ & Output \ RESET \ V_{OL} \ @ \ ICRD_rst = +200 \ \muA \\ & Output \ RESET \ Rise \ Time \ @ \ C_{out} = 30 \ pF \\ & Output \ RESET \ Fall \ Time \ @ \ C_{out} = 30 \ pF \end{array}$                                                              | 0.9 * CRD_V <sub>CC</sub><br>0            |     | CRD_V <sub>CC</sub><br>0.3<br>0.8<br>0.8     | V<br>V<br>μs<br>μs        |

| 5,16 | CRD_CLKA<br>CRD_CLKB    | $\begin{array}{l} \mbox{CRD}\_V_{CC} = +3 \ V \\ \mbox{Output Duty Cycle} \\ \mbox{Max Output Frequency} \\ \mbox{Output V}_{OH} @ \ ICRD\_clk = -20 \ \mu A \\ \mbox{Output V}_{OL} @ \ ICRD\_clk = +200 \ \mu A \\ \mbox{Output CRD}\_CLK \ Rise \ Time \ @ \ C_{out} = 30 \ pF \\ \mbox{Output CRD}\_CLK \ Fall \ Time \ @ \ C_{out} = 30 \ pF \end{array}$ | 40<br>5<br>0.9 * CRD_V <sub>CC</sub><br>0 |     | 60<br>CRD_V <sub>CC</sub><br>0.3<br>18<br>18 | %<br>MHz<br>V<br>ns<br>ns |

|      |                         | $\begin{array}{l} {\sf CRD\_V_{CC}=+1.8\ V}\\ {\sf Output\ Duty\ Cycle}\\ {\sf Max\ Output\ Frequency}\\ {\sf Output\ V_{OH}\ @\ ICRD\_clk=-20\ \mu A}\\ {\sf Output\ V_{OL}\ @\ ICRD\_clk=+200\ \mu A}\\ {\sf Output\ CRD\_CLK\ Rise\ Time\ @\ C_{out}=30\ pF}\\ {\sf Output\ CRD\_CLK\ Fall\ Time\ @\ C_{out}=30\ pF} \end{array}$                           | 40<br>5<br>0.9 * CRD_V <sub>CC</sub><br>0 |     | 60<br>CRD_V <sub>CC</sub><br>0.3<br>18<br>18 | %<br>MHz<br>V<br>ns<br>ns |

| 7,14 | CRD_I/OA<br>CRD_I/OB    | $\begin{array}{l} CRD\_V_{CC}=+3 \ V\\ Output \ V_{OH} \ @ \ I_{CRD\_IO}=-20 \ \mu\text{A}, \ V_{I/O}=V_{DD}\\ Output \ V_{OL} \ @ \ I_{CRD\_IO}=+1 \ m\text{A}, \ V_{I/O}=0 \ V\\ CRD\_I/O \ Rise \ Time \ @ \ C_{out}=30 \ p\text{F}\\ CRD\_I/O \ Fall \ Time \ @ \ C_{out}=30 \ p\text{F} \end{array}$                                                      | 0.8 * CRD_V <sub>CC</sub>                 |     | CRD_V <sub>CC</sub><br>0.4<br>0.8<br>0.8     | V<br>V<br>μs<br>μs        |

|      |                         | $\begin{array}{l} \mbox{CRD}\_V_{CC} = +1.8 \ V \\ \mbox{Output } V_{OH} @ \ I_{CRD}\_IO = -20 \ \mu A, \ V_{I/O} = V_{DD} \\ \mbox{Output } V_{OL} @ \ I_{CRD}\_IO = +1 \ mA, \ V_{I/O} = 0 \ V \\ \mbox{CRD}\_I/O \ Rise \ Time \ @ \ C_{out} = 30 \ pF \\ \mbox{CRD}\_I/O \ Fall \ Time \ @ \ C_{out} = 30 \ pF \end{array}$                                | 0.8 * CRD_V <sub>CC</sub><br>0            |     | CRD_V <sub>CC</sub><br>0.3<br>0.8<br>0.8     | V<br>V<br>μs<br>μs        |

|      |                         | Short–Circuit Current, $V_{I/O} = 0 V$                                                                                                                                                                                                                                                                                                                         |                                           | 4   | 15                                           | mA                        |

| 8    | R <sub>pu_CRD_I/O</sub> | Card I/O Pullup Resistor                                                                                                                                                                                                                                                                                                                                       | 10                                        | 14  | 18                                           | kΩ                        |

NOTE: Device will meet the specifications after thermal equilibrium has been established when mounted in a test socket or printed circuit board with maintained transverse airflow greater than 500 lfpm. Electrical parameters are guaranteed only over the declared operating temperature range. Functional operation of the device exceeding these conditions is not implied. Device specification limit values are applied individually under normal operating conditions and not valid simultaneously.

3. All the dynamic specifications (AC specifications) are guaranteed by design over the operating temperature range.

# **TYPICAL CHARACTERISTICS**

# **APPLICATION INFORMATION**

The NCN4557 is a dual LDO–based DC/DC converter and level shifter able to handle independently 2 smart card interfaces. When one of these interfaces is operating the other one is not active and conversely. Class B (3.0 V) and C (1.8 V) cards can be used.

The Card and the CRD\_V<sub>CC</sub> power supply are selected using the pins SEL0, SEL1 and ENABLE according to Table 1.

| ENABLE | SEL1 | SEL0 | Card# / CRD_V <sub>CC</sub> |

|--------|------|------|-----------------------------|

| 1      | 0    | 0    | Card A / 1.8 V              |

| 1      | 0    | 1    | Card A / 3.0 V              |

| 1      | 1    | 0    | Card B / 1.8 V              |

| 1      | 1    | 1    | Card B / 3.0 V              |

| 0      | Х    | Х    | A & B Disabled              |

#### Table 1. CARD AND CRD\_V<sub>CC</sub> SELECTION

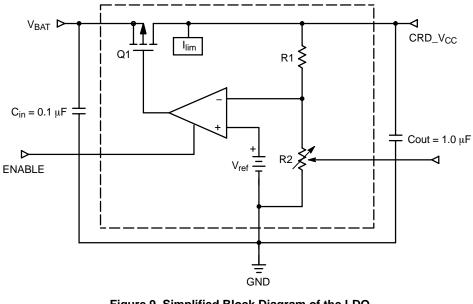

# Card Supply Converter

The built–it NCN4557 DC/DC converters are Low Drop–Out Voltage Regulators capable to supply a current in excess of 50 mA under 1.8 V or 3.0 V. These voltages are selected according to Table 1. Using the Boolean input ENABLE pin the NCN4557 device can be disabled setting the circuit in a shutdown mode for which the power consumption features values typically in the range of a few tens of nA. Figure 9 shows a simplified view of the NCN4557 voltage regulator. The CRD\_V<sub>CC</sub> output is internally current limited and protected against short circuits. The short–circuit current IV<sub>CC</sub> varies with V<sub>BAT</sub> typically in the range of 30 mA to 60 mA.

In order to guarantee a stable and satisfying operating of the LDO the CRD\_V<sub>CC</sub> output will be connected to a 1.0  $\mu$ F bypass ceramic capacitor to the ground. At the input, V<sub>BAT</sub> will be bypassed to the ground with a 0.1  $\mu$ F ceramic capacitor.

Figure 9. Simplified Block Diagram of the LDO Voltage Regulator

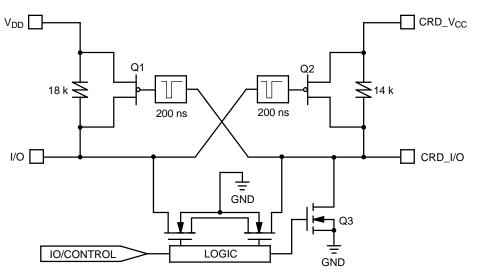

#### Level Shifters

The level shifters accommodate the voltage difference that might exist between the microcontroller and the smart card. The RESET and CLOCK level shifters are mono-directional and feature both the same architecture.

The bidirectional I/O line provides a way to automatically adapt the voltage difference between the

controller and the card in both directions. In addition with the pull–up resistor, a dynamic pullup circuit (Figure 10, Q1 and Q2) provides a fast charge of the stray capacitance, yielding a rise time fully within the ISO7816, EMV and GSM specifications.

Figure 10. Basic I/O line Interface

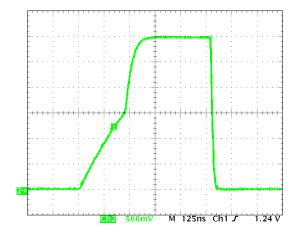

The typical waveform provided in Figure 11 shows how the accelerator operates. During the first 200 ns (typical), the slope of the rise time is solely a function of the pullup resistor associated with the stray capacitance. During this period, the PMOS devices are not activated since the input voltage is below their  $V_{gs}$  threshold. When the input slope crosses the  $V_{gsth}$ , the opposite one shot is activated, providing a low impedance to charge the capacitance, thus increasing the rise time as depicted in Figure 11. The same mechanism applies for the opposite side of the line to make sure the system is optimum.

Figure 11. CRD\_IO Typical Rise and Fall Times with Stray Capacitance > 30 pF (33 pF capacitor connected on the board)

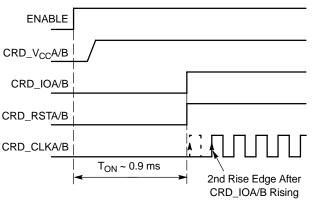

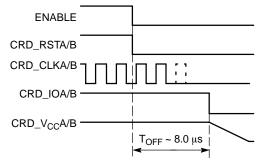

### **Powerup Sequence**

The powerup sequence makes sure all the card-related signals are LOW during the  $CRD_V_{CC}$  positive going slope. The Powerup sequence is activated by setting the ENABLE Boolean signal HIGH. CRD\_RST, CRD\_CLK and CRD\_I/O are maintained LOW during the activation stage until CRD\_V\_{CC} reaches its nominal value (1.8 V or

3.0 V). Figure 7 shows the typical NCN4557 activation sequence.

About 800  $\mu$ s after CRD\_V<sub>CC</sub> has reached its nominal voltage value, CRD\_IO and CRD\_RST are released.

CRD\_CLK is enabled during the rising slope of the second clock cycle after CRD\_IO and CRD\_RST are enabled.

In all cases the application software is responsible for the smart card signal sequence (contact activation sequence, cold reset and warm reset sequences).

#### **Powerdown Sequence**

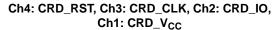

The NCN4557 provides a powerdown sequence which is activated by setting the ENABLE Boolean signal LOW. The communication I/O session is terminated immediately according to the ISO7816 and EMV specifications as depicted in Figures 8 and 13.

ISO7816 Sequence:

- CRD\_RST is forced to LOW

- CRD\_CLK is forced to LOW 2 clock cycles after ENABLE is set LOW unless CRD\_CLK is already in

this state or 8  $\mu s$  after the ENABLE pin is set LOW in the other cases.

- CRD\_I/O is forced to LOW about 8 µs after the ENABLE pin is set LOW.

- Then CRD\_V<sub>CC</sub> Supply Shuts Off

Figure 13. NCN4557 Power Down Sequence

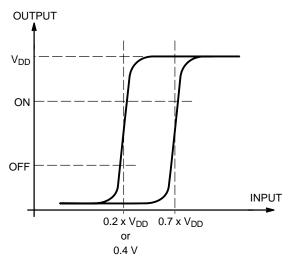

#### **Input Schmitt Triggers**

All the logic input pins (excepted I/O and CRD\_I/O, Figure 3) have built–in Schmitt trigger circuits to prevent the NCN4557 against uncontrolled operation. The typical dynamic characteristics of the related pins are depicted in Figure 14.

Figure 14. Typical Schmitt Trigger Characteristics

#### ORDERING INFORMATION

# Shutdown Operating

In order to save power or for other purpose required by the application it is possible to put the NCN4557 in a shutdown mode by setting LOW the pin ENABLE. On the other hand the device enters automatically in a shutdown mode when  $V_{DD}$  becomes lower than 1.0 V typically.

#### **ESD** Protection

The NCN4557 CRD interface features an Human Body Model ESD voltage protection in excess of 8 kV for all the CRD pins (CRD\_IOA & B, CRD\_CLKA & B, CRD\_RSTA & B, CRD\_V<sub>CC</sub>A & B and GND). All the other pins (microcontroller side) sustain at least 2 kV. These values are guaranteed for the device in its full integrity without considering the external capacitors added to the circuit for a proper operating. Consequently in the operating conditions it is able to sustain much more than 8 kV on its CRD pins making it perfectly protected against electrostatic discharge well over the Human Body Model ESD voltages required by the ISO7816 standard (4 kV).

#### Printed Circuit Board Layout

Careful layout routing will be applied to achieve a good and efficient operating of the device in its mobile or portable environment and fully exploit its performance.

The bypass capacitors have to be connected as close as possible to the device pins (CRD\_V<sub>CC</sub>A and B, V<sub>DD</sub> or V<sub>BAT</sub>) in order to reduce as much as possible parasitic behaviors (ripple and noise). It is recommended to use ceramic capacitors.

The exposed pad of the QFN–16 package will be connected to the ground. A relatively large ground plane is recommended.

| Device       | Package             | Shipping <sup>†</sup> |

|--------------|---------------------|-----------------------|

| NCN4557MTG   | QFN-16<br>(Pb-Free) | 123 Units / Rail      |

| NCN4557MTR2G | QFN-16<br>(Pb-Free) | 3000 / Tape & Reel    |

+For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

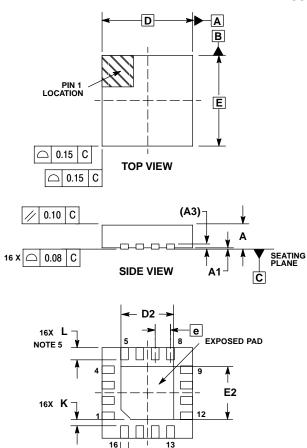

#### PACKAGE DIMENSIONS

QFN16 3\*3\*0.75 MM, 0.5 P CASE 488AK-01 ISSUE O

**BOTTOM VIEW**

NOTES:

- DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

- CONTROLLING DIMENSION: MILLIMETERS.

DIMENSION b APPLIES TO PLATED TERMINAL AND IS MEASURED BETWEEN

- TERMINAL AND IS MEASURED BETWEEN 0.25 AND 0.30 MM FROM TERMINAL. 4. COPLANARITY APPLIES TO THE EXPOSED

- COPLANARITY APPLIES TO THE EXPOSED PAD AS WELL AS THE TERMINALS.

L<sub>max</sub> CONDITION CAN NOT VIOLATE 0.2 MM

- L<sub>max</sub> CONDITION CAN NOT VIOLATE 0.2 MM SPACING BETWEEN LEAD TIP AND FLAG.

|     | MILLIMETERS |      |  |  |

|-----|-------------|------|--|--|

| DIM | MIN         | MAX  |  |  |

| Α   | 0.70        | 0.80 |  |  |

| A1  | 0.00        | 0.05 |  |  |

| A3  | 0.20        | REF  |  |  |

| b   | 0.18        | 0.30 |  |  |

| D   | 3.00        | BSC  |  |  |

| D2  | 1.65        | 1.85 |  |  |

| E   | 3.00        | BSC  |  |  |

| E2  | 1.65        | 1.85 |  |  |

| е   | 0.50 BSC    |      |  |  |

| к   | 0.20        |      |  |  |

| L   | 0.30        | 0.50 |  |  |

ON Semiconductor and I are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters, including "Typicals" must be validated for each customer applications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use personal injury or death design or manufacture of the part. SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### PUBLICATION ORDERING INFORMATION

16X b

CAB

0.10

⊕ 0.05 C NOTE 3

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303–675–2175 or 800–344–3860 Toll Free USA/Canada Fax: 303–675–2176 or 800–344–3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800–282–9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81–3–5773–3850 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative